While one of the new DSP PHYs reportedly offers the industry’s lowest power consumption for 800G, the other is the first 200G/lane DSP with integrated VCSEL drivers.

This week, Broadcom expanded its existing DSP PHY lineup to include new solutions for AI/ML clusters. All About Circuits interviewed Natarajan Ramachandran, director of product line management for Broadcom’s Physical Layer Products Division, to learn more about the products firsthand.

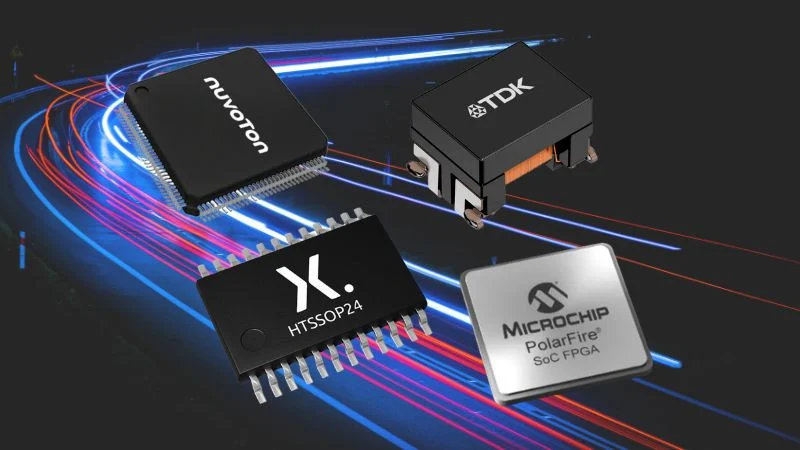

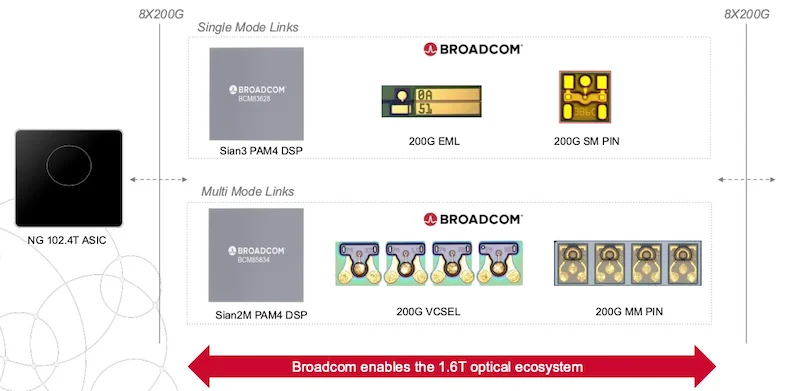

Broadcom's optical sub-component offerings.

Sian3 DSP (BCM83628)

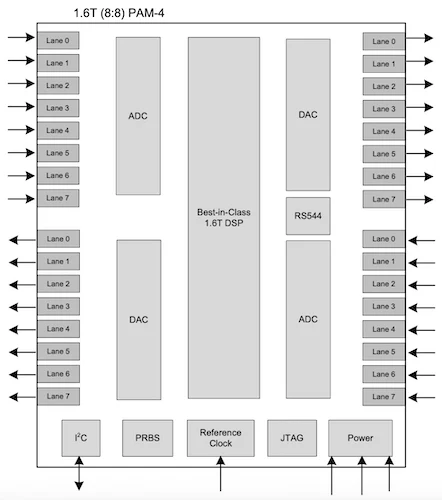

The Broadcom BCM83628-DIE is a monolithic 3 nm CMOS transceiver PHY. It integrates eight 200-G PAM-4 SerDes lanes with embedded laser drivers to deliver 1.6 Tbps throughput in OSFP DR8 and FR8 transceivers.

“The DSP driver and TIA traditionally have been three different subcomponents on a PCB,” Ramachandran said. “What we did was integrate the driver into our chip. And when this happens, there are a lot of things you can do in terms of design innovation.”

With this integration, the device supports client-to-line 8:8 re-timer operation at 212.5 Gb/s per lane. It includes an option to convert to 226.875 Gb/s for compatibility with InfiniBand XDR, in addition to backward compatibility with 106 G and 53 G per-lane Ethernet and InfiniBand. The PHY also incorporates Broadcom's low-power, high-efficiency digital signal processing and equalization architecture, which operates within the IEEE 802.3dj D1p3 standard. These DSP capabilities correct channel impairments to minimize bit error rates and optimize signal integrity across high-density optical interconnects.

Block diagram of the BCM83628.

The transceiver also includes integrated electro-absorption modulated lasers (EMLs) and silicon photonics (SiPh)-compatible laser drivers to reduce system-level complexity and power draw. It operates using a 625 MHz reference clock and internally synthesizes high-frequency, low-jitter clocks using phase-locked loops. The client and line sides both include flexible crossbar routing to ease PCB layout and improve signal trace optimization in OSFP modules.

To support low-latency transmission in hyperscale Ethernet and AI/ML cluster environments, the device supports multiple line-side FEC schemes, including KP4, segmented, concatenated, and full FEC bypass.

Sian3 DSP (BCM83820)

The new BCM83820-DIE is a monolithic 800-G (8:4) PAM-4 DSP transceiver PHY fabricated in a 3 nm CMOS process.

Similar to the BCM83628, the device integrates a laser driver and supports both 212.5 Gb/s and 226.875 Gb/s line-side signaling to interface with EMLs and SiPh optics. Importantly, the device converts eight 106.25 Gb/s PAM-4 client-side electrical lanes into four higher-rate PAM-4 optical lanes. As such, this gearbox architecture targets OSFP DR4 and FR4 modules in 800-G Ethernet and InfiniBand XDR deployments.

Application diagram of the BCM83820-DIE.

The device also leverages Broadcom’s 200-G/lane SerDes and DSP architecture, sharing design lineage with the BCM85828-DIE. It incorporates a high-performance equalization engine and DSP to compensate for optical distortions and maintain a low bit error rate (BER) at reduced power.

“The SerDes facing the optics is a different SerDes because it's built for managing the optical impairments, the noise, the ring noise, and the non-linearity that the optics introduce,” Ramachandran said.

The PHY also integrates a differential high-swing, 3.0 V laser driver to support SiPh optical modulators. It includes multiple forward error correction (FEC) schemes such as bypass, segmented, and concatenated modes to maintain signal integrity across varying link budgets. The chip also provides IEEE 802.3cd KP4 FEC support and optional end-to-end FEC bypass to accommodate interoperability with Ethernet and InfiniBand infrastructures.

Sian2M DSP (BCM85834)

The Broadcom BCM85834-DIE is a monolithic 5-nm CMOS transceiver PHY that supports 800-G (4×200G) PAM-4 signaling with an integrated vertical-cavity surface-emitting laser (VCSEL) driver. It converts four 212.5 Gb/s PAM-4 lanes from the client interface to four 212.5 Gb/s PAM-4 lanes on the line side to support next-generation multimode fiber (MMF) optical links.

The new PHY devices target high-speed optical networks.

To meet the performance demands of 200G/lane operation, the PHY incorporates fourteen-tap transmit finite impulse response (TX FIR) filters on both client and line sides. It supports IEEE 802.3cd KP4 forward error correction and can operate in FEC bypass or segmented FEC mode to minimize latency. With a total latency of 80 ns, the PHY represents one of the lowest latency options in its class.

The integrated VCSEL driver reduces system complexity and improves transmitter performance within OSFP modules. Ramachandran noted that this chip addresses existing challenges facing VCSEL implementations.

“We are throwing heavy, sophisticated signal processing techniques into our chip to compensate or precompensate for VCSEL impairments,” he said.

Broadcom claims this approach preserves signal integrity across short-reach links while mitigating the bandwidth limitations of 200-G VCSELs.

Broadcom Pushes the Envelope on Lower Watts

“We started at 28 watts, and we'll bring our solutions down to 23 watts this year,” Ramachandran reflected. “We're basically showing the industry a roadmap of how we can get to below sub-20 watts by sometime next year. Eventually getting to 10 watts is very, very challenging at 1.60 Tbps, but we believe there is a path forward.”

Broadcom is now sampling Sian3 (BCM83628 and BCM83820) and Sian2M (BCM85834) to early access customers and partners. The company expects to begin Sian3 production at scale in Q3 2025.

All images used courtesy of Broadcom.