Intel Launches New Data Center Processor Family at Computex 2024

The new processors promise 3:1 rack consolidation, 4.2x rack-level performance gains, and 2.6x performance per watt gains.

Intel announced its newest data center processor family, the Xeon 6, at Computex 2024. The new processors come in either Performance-core (P-core) or Efficient-core (E-core) variants to serve applications requiring the highest levels of performance and those focused on hardware density and power conservation.

Computing performance today isn’t just about brute-force computation. While heavy-duty computing power is vital, with a typical mid-size data center having about 200 racks and consuming about 15 Kilowatts of power, energy consumption is equally critical. The Xeon 6 architecture is built to tackle both needs.

Intel Xeon 6 processor for high-density data center applications.

The new E-core processors promise a three-to-one rack consolidation, allowing up to 4.2x performance per unit of rack space and 2.6x performance per watt. According to Matt Langman, Intel VP and general manager for Intel Xeon 6 processors with P-cores, the Xeon 6 E-core processors will enable the same computation output in a third of the space. That level of efficiency shrinks the physical and carbon footprints of an installation or increases the throughput of a same-size installation.

The ecosystem-compatible P-core is optimized for AI and other high-intensity data center applications. P-core is designed to operate alongside Intel Gaudi AI accelerators. Intel hopes to stack the Xeon 6 P-core/Gaudi combination up against the Nvidia H100 AI large language model (LLM) training architecture.

Advanced Memory Interface

Compute Express Link (CXL) is critical to data center applications, and Xeon 6 was built from the start with it in mind. CXL is a high-capacity CPU-to-device and CPU-to-memory open interconnect specification. It’s built on serial PCI Express (PCIe) interface technology. Intel created the CXL standard consortium in 2019. Competing high-speed data center interconnect standards have since been merged into the CXL specification.

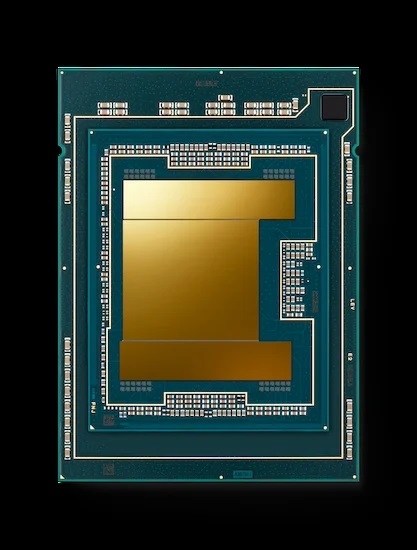

Xeon 6 Efficient-core processor

"We're trying to achieve greater than 2x over the prior generation Xeon,” said Intel senior fellow Sailesh Kottapalli. “We wanted to make sure that we also provision similar memory bandwidth increase to go with it to support the performance scalability.”

Xeon 6 includes support for CXL I, II, and III for maximum performance and flexibility. The Xeon 6 natively supports 12 channels of memory, both DDR at multi-ranked buffered dual inline memory module (MR-DIM). With CXL III hetero interleave mode, the Xeon adds four more memory channels for an effective 16 channels. This expansion is completely software-transparent.

Chiplets Allow Greater Design Flexibility

The Xeon 6 chip is constructed out of a set of smaller chiplets. One of the advancements that come with the Xeon 6 multi-die architecture is a manufacturing optimization that uses different process nodes for the chiplets based on functional requirements. The way the I/O and compute are partitioned is significant, says Kottapalli.

“We have a partitioning where a lot of the I/O capability utilities are aggregated in a silicon construct, which is optimized on one technology node. The rest of the compute, along with the optimized memory support, is on a different technology node that brings in the most performance as well as power efficiency.”

E-core vs. P-core

As highlighted above, the E-core (code-named Sierra Forest) is focused on space and energy efficiency, while the P-core (code-named Granite Rapids) is targeted at the highest-demand data center applications, such as AI and scalable cloud-native applications.

Xeon 6 Performance-core processor.

While the two processors share the same interface architecture, the P-core has additional compute chiplets integrated. The platform is designed with expansion in mind. For I/O, the architecture will allow up to 136 PCIe lanes, and P-core will eventually support up to 128 cores. The E-core processors are available now, and the P-core is projected to be available in Q3 2024.

More on Lunar Lake to Come...

In addition to the Xeon 6 announcement, Intel also unveiled the Lunar Lake x86 AI PC architecture. Intel expects Lunar Lake to reduce system-on-chip (SoC) cost by up to 40% over the previous-generation x86 client architecture.

Lunar Lake enables new performance cores (P-cores) for desktop and high-performance systems and efficient cores (E-cores) for power-constrained applications in the mobile and laptop arena. It includes a fourth-generation neural processing unit (NPU) and Battlemage, an all-new GPU design.

Stay tuned to All About Circuits for more details about the Lunar Lake architecture.

.jpg)

.jpg)