Memory Leaders Rise to Meet the Storage Challenges of AI

At this year's Future of Memory and Storage show, Microchip, Micron, and Samsung presented new memory solutions in the age of AI—from SSD controllers to LPDDR5X DRAM.

This year’s Future of Memory and Storage (FMS) conference, previously known as the Flash Memory Summit, saw exciting announcements from leading industry players like Microchip, Micron, and Samsung. Each announced memory devices that promise to improve performance, capacity, and energy efficiency.

.jpg)

Microchip, Micron, and Samsung each presented new memory technologies at FMS.

This demand for advanced memory and storage solutions is at a fever pitch as smartphones, autonomous vehicles, and even data centers tackle burgeoning AI workloads. Here's a look at how the three companies proposed to address these challenges at the FMS conference.

Microchip’s Gen 5 SSD Controllers

Microchip recently released its Flashtec NVMe 5016, a high-performance PCIe Gen 5 Flash controller designed for enterprise and data center applications. At its core, the 5016 features a flexible and programmable architecture that gives developers precise control over NVMe SSD performance for a wide range of demanding workloads, from cloud computing and business-critical applications to AI-focused data movement tasks.

.jpg)

The Flashtec architecture diagram. Image used courtesy of Microchip

This controller supports 16 independent Flash channels, which accommodate a wide array of NAND technologies, including SLC, MLC, TLC, and QLC, with Toggle and ONFI interfaces up to 3,200 MT/s. Featuring a power-optimized design, the controller combines architectural and semiconductor advances to deliver over 2.5 GB/W of data and up to 3.5 million random-read IOPS. The chip also supports the latest NVMe 2.0+ protocol and can achieve over 14 GB/s of bandwidth via a PCIe Gen 5 x 4 or dual x2 host interface. To support these high rates while keeping power low, the chip provides advanced power management features, including automatic idling of processor cores and autonomous power reduction capabilities.

Microchip has also integrated its advanced ECC engine into the 5016, which leverages both hard and soft decode LDPC techniques to provide endurance and reliability for NAND Flash, including QLC. This is complemented by end-to-end data security and integrity features like secure boot, dual signature authentication, encryption, and sophisticated key management.

Micron’s PCIe Gen 6 SSD

At this year’s Future of Memory Storage, Micron announced and demonstrated its first PCIe Gen6 data center SSD.

While much is still unknown about the SSD, Micron has revealed that it architecturally designed the device around Micron’s latest high-performance NAND Flash memory, coupled with a high-bandwidth PCIe Gen6 interface. This combination allows the SSD to deliver unparalleled data throughput for data-intensive applications, such as sequential read bandwidths exceeding 26 GB/s. With the ability to ingest and process vast amounts of data at high speeds, the new SSD can support AI-related tasks such as training large models and accelerating inference.

.jpg)

Micron claims its 9550 NVMe SSD, a separate SSD from this announcement, is the "world’s fastest data center SSD". Image used courtesy of Micron

In addition to its raw performance capabilities, Micron claims its PCIe Gen6 SSD also focuses on power efficiency. By optimizing the SSD's power consumption characteristics, Micron aims to enable more efficient AI and computing solutions for the already power-hungry data center. Additionally, the SSD will incorporate advanced error correction and data protection mechanisms.

Samsung’s LPDDR5x DRAM

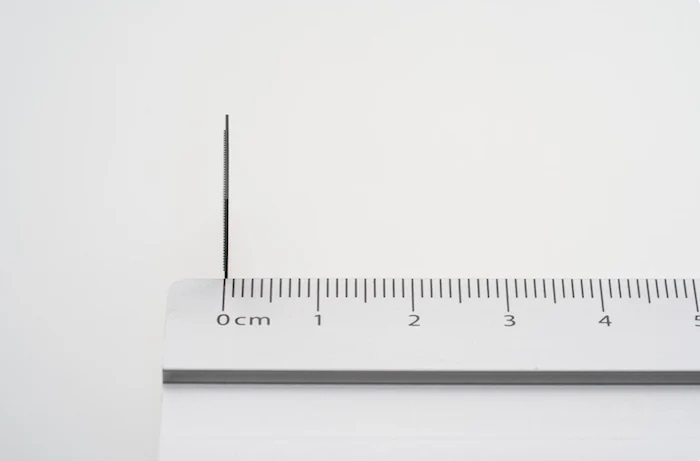

Samsung recently announced the mass production of its LPDDR5X DRAM. The LPDDR5X DRAM's architectural innovations include a four-layer stacking of 12 nm-class DRAM dies, enabling an ultra-thin package height of just 0.65 mm. According to Samsung, this compact design facilitates better thermal control and enhances heat resistance by approximately 21.2%.

The packaging technique involves advanced PCB and epoxy molding compound (EMC) processes, which protect the semiconductor circuits from external stressors such as heat and moisture. Samsung's optimized back-lapping process further reduces the package height.

.jpg)

The LPDDR5X is 0.65 mm in height. Image used courtesy of Samsung

The new solution achieves data processing speeds up to 10.7 Gbps. In terms of power efficiency, the solution incorporates full dynamic voltage frequency scaling (FDVFS) and low-frequency mode extension. These technologies collectively reduce power consumption by nearly 25% compared to their predecessors, thereby extending the battery life of mobile devices and reducing the total cost of ownership through lower carbon emissions.

Samsung claims the new LPDDR DRAM package is as thin as a fingernail. Image use courtesy of Samsung

The new DRAM modules come in capacities of 12 GB and 16 GB, with plans for future expansions to 24-GB and 36-GB modules in six-layer and eight-layer stacks.

Storage for the Next Era of Computing

These SSD and DRAM solutions from Microchip, Micron, and Samsung demonstrate a cross-industry push to support the next era of computing. As emerging workloads like AI, cloud computing, and autonomous vehicles test the boundaries of current storage and memory technologies, we may continue to see more vertical memory architectures, greater DDR5 adoption, lower power consumption, and more sustainable manufacturing efforts.

.jpg)