SiTime Trumpets New Integrated Clock Chip as a First for AI Data Centers

The new SiTime data center clock chip delivers 10x higher performance than quartz crystal-based devices in half the space.

At Embedded World 2024, SiTime introduced Chorus, its latest data center-targeted clock generator family. The MEMS-based Chorus clock system-on-chip (ClkSoC) is the first integrated clock generator designed for artificial intelligence data center installations.

The chip uses a silicon MEMS resonator at its heart rather than a quartz crystal. Quartz, long the industry standard for precision timing, is often running near its limits under the operating conditions found in large data centers such as those used for generative AI large language model (LLM) stacks. The MEMs resonator driving Chorus is better suited to thrive in a hot, electrically noisy data center environment.

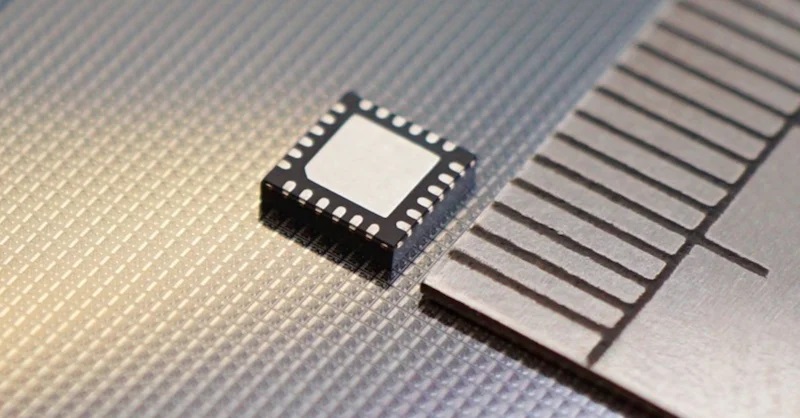

SiT91213 and SiT91211 4 x 4 mm 24-pin QFN package.

Chorus integrates the MEMS resonator, oscillator circuitry, and a clock IC into a single chip. This eliminates the need for external crystals and greatly simplifies system clock architecture. This reduces design time, parts count, and PCB real estate while improving manufacturability, reliability, and system performance.

Key Features of Chorus

The Chorus clock generator chips come in a 24-pin 4 mm x 4 mm, 0.5-mm-pitch QFN with wettable flanks. The small size enables greater PCB layout flexibility, and the small-pitch QFN with wettable flanks delivers consistent manufacturability, efficient component cooling, and long-time reliable operation.

Compared to quartz crystal-based devices, the SiT91213 or SiT91211 deliver 10x better resilience during operation with the MEMS resonator. The parts have very low jitter, programmable frequency outputs, and strong frequency stability (±20 ppm and ±50 ppm from -40°C to 105°C).

A single SiT91213 or SiT91211 can replace multiple standalone oscillators (left) with their ability to drive four differential loads or eight single-ended loads (right).

The two chips are identical except in jitter specifications:

The parts have an adjustable frequency range from 1 MHz to 700 MHz, a configurable clock domain, and four differential or eight single-ended outputs. The clock outputs can be driven as LVDS, HCSL, LVPECL, or LVCMOS.

SiTime Rises to Meet Data Center Clocking Needs

Although every high-speed device requires high-quality clocking, data centers operate under thermal and electrical noise conditions that push well past the requirements for most independent systems. Data centers move and process massive amounts of data across many clock and physical domains. Data must synchronize across high-speed, in-chip interconnects, chip-to-chip busses, and inter-device busses. Jitter, slew, and drift are even more important in such a critical environment.

SiTime has a long history of producing precision timing devices, focusing particularly on performance over legacy technology. While traditional timing circuits use a discrete quartz crystal or hybrid crystal oscillator device as the primary high-precision frequency standard, the Chorus timer chips dispense with quartz and the external source.

iT91213 and SiT91211 internal block diagram.

SiTime developed a silicon MEMS frequency source that exceeds the performance of quartz crystals and can be easily integrated with other key components into an SoC. The SiTime chips combine the MEMS resonator with the oscillator circuit, PLL, clock distribution, and driver circuitry. It also adds GPIO and I2C/SPI for communications and control.

According to SiTime, the result of this advanced integration is a unified multi-output clock source that can reduce the PCB footprint by 50% due to the reduced parts count and the ability to replace four separate oscillator circuits with one chip.

Development Tools and Availability

SiTime offers the SiT6520EB Evaluation Board to jump-start system design and learning. The chips are shipping now (April 2024) to strategic customers and are expected to ship for general availability in the second half of 2024.