AMD Reveals Adaptive SoCs With RF Conversion and 80 TOPS DSP

Announced today, the new series integrates RF-sampling converters and high-performance compute on a single chip.

Today, AMD expanded its adaptive system-on-chip (SoC) portfolio with the launch of the Versal RF series. The highly integrated solution includes compute and built-in RF converters, with its target applications in the aerospace and defense and test and measurement markets.

.jpg)

A rendering of the AMD Versal RF solution.

All About Circuits spoke to AMD representatives David Brubaker and Manuel Uhm to learn more about the new series firsthand.

DSP Compute for the RF Edge

AMD designed the Versal RF series to tackle the growing complexity of RF systems through precise, wide-spectrum signal capture.

“Today’s RF systems are not just about voice anymore; you need to process video, imagery, and other high-bandwidth data,” Uhm explained. “This means operating at higher frequencies and sample rates while maintaining the computing power to handle it.”

To this end, the series integrates high-resolution RF-sampling data converters, AI engines, and dedicated DSP hard IP into a single monolithic device. The device’s compute is centered around a dual-core Arm Cortex-R5F real-time processor and a dual-core Arm Cortex-A74 application processor. The compute cluster is supported by 6400-DDR5 and 8533-LPDDR5x with selectable inline encryption. Meanwhile, the integrated AI engines for DSP can run up to 32 giga-multiple and accumulates (GMACs) each at 1.3 GHz.

.jpg)

Functional block diagram of the Versal RF series. (Click on image to enlarge)

The Versal RF series introduces massive DSP compute capabilities. With up to 80 trillion operations per second (TOPS) of DSP capability and support for frequencies up to 18 GHz, these devices deliver up to 19 times the performance of AMD’s previous Zynq UltraScale+ RFSoC Gen3 products. The device also includes dedicated hard IP blocks, such as FFT/iFFT and polyphase arbitrary resamplers, to enable complex signal processing directly on the chip. Such an architecture minimizes latency by processing data immediately after digitization—a major boon in applications such as phased-array radar and wideband spectrum analysis. More information is available in the Versal RF product brief.

On-Chip RF Resources

A notable achievement for Versal RF was the successful implementation of RF and digital on the same chip.

“People doubted we could manage digital noise and analog performance on the same monolithic chip, but through detailed isolation strategies and innovative design, we proved it’s possible,” Brubaker said.

The Versal RF series integrates 32 gigasamples per second (GSPS) of RF analog-to-digital converters (ADCs) with 14-bit resolution and direct sampling capabilities for frequencies up to 18 GHz. Combined with the devices’ ability to digitize up to 18 GHz of bandwidth in a single step, this feature ensures that users can capture and process high-frequency, wide-spectrum signals without requiring additional components.

The system also features hard digital up- and down-conversion blocks on the chip, enabling agile frequency selection and signal characterization. These blocks provide flexibility when dynamically tuning to specific frequencies. AMD included channelizers to precisely separate signals into sub-bands for high-resolution signal analysis.

Power Efficiency Through Hard IP and Monolithic Integration

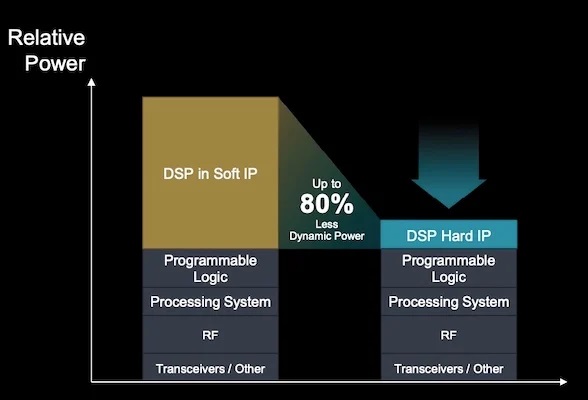

A defining feature of the Versal RF series is its focus on power efficiency, achieved by strategically using hard IP for computationally intensive tasks. According to AMD, implementing DSP functions such as FFTs and LDPC decoders in hard IP reduces power consumption by up to 80% compared to traditional soft logic implementations.

AMD claims that hard IP reduces dynamic power by up to 80%.

The monolithic integration of analog and digital components further contributes to efficiency. By eliminating chip-to-chip interfaces, such as JESD204 links, the devices avoid additional power overhead associated with high-speed interconnects. This integration also reduces latency since data no longer needs to traverse multiple chips for processing. AMD also claims that the single-chip design simplifies the system architecture and improves signal integrity by reducing potential noise and interference.

.jpg)